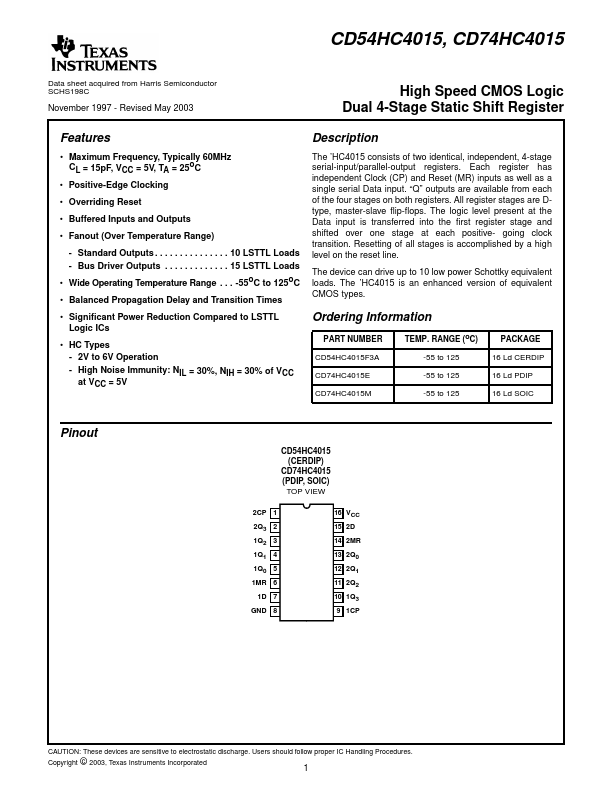

CD54HC4015 Overview

Key Specifications

Package: CDIP

Mount Type: Through Hole

Pins: 16

Max Voltage (typical range): 6 V

Description

Maximum Frequency, Typically 60MHz CL = 15pF, VCC = 5V, TA = 25oC - Positive-Edge Clocking - Overriding Reset - Buffered Inputs and Outputs - Fanout (Over Temperature Range) - Standard Outputs. Wide Operating Temperature Range.